- 头条多电压与扫描链技术在芯片设计中的应用导语针对芯片中功耗高、测试成本较高的问题,福州大学物理与信息工程学院的研究人员向韬鑫、王仁平、刘东明、陈荣林,在2020年第6期《电气技术》杂志上撰文,以一款乘加器为例,该乘加器可以切换在乘、加、乘加3种工作状态。在芯片设计过程中,利用统一标准格式技术实现多电压设计达到低功耗的效果,利用扫描链技术,完成可测试性设计,降低芯片的测试成本,并解决了两种技术的兼容性问题。

5G通信和物联网时代即将到来,各类芯片不断高性能化,设计规模也不断变大。而近年逐渐失效的摩尔定理,很难使芯片的价格和工艺尺寸同时减小,因此在实现高性能的同时,节约功耗和降低生产成本越来越受关注。对于数字信号处理芯片,乘、加、乘加算法都是其较为常见的运算模块,将3种算法整合在一起,并使其可以自由切换工作状态,能较大地节省面积成本。

除此之外,低功耗技术设计和可测试性设计(desgin for test, DFT)技术也可以降低芯片功耗成本和测试成本。利用统一标准格式(unified power format, UPF)实现多电压技术。根据不同模块性能需求,在芯片内划分不同的电压域(power domain)进行分割处理,实现低功耗设计。

而DFT中的扫描链技术(scan chain)可以在短时间内检查芯片内部各寄存器的好坏,早一步将因工艺缺陷和尘埃附着的损坏芯片在裸片阶段检测出来,可以防止损坏的芯片流入下一阶段的设计中而造成更大损失。

1 电路设计

1.1 电路逻辑设计

加、乘、乘加是数字处理芯片常见的3种算法,但芯片内3种算法都在满负荷同时工作的状态中的情况并不多见,因此在芯片中插入一些可切换状态,并整合了3种功能的乘加器,随芯片的工作需要,调整芯片的工作状态,可以节省面积。

本设计中以二输入的mode信号作为控制信号,mode信号通过控制数据选择器,来控制在各模块输入和顶层输出端的采样,最终来控制乘加器工作状态,如图1所示。

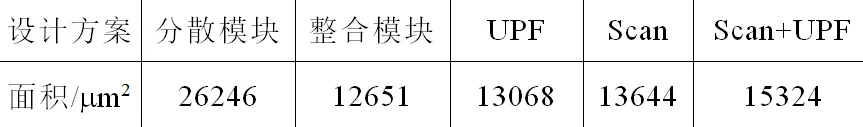

输入mode分别在00、01、10、11时,乘加器分别切换到乘、加、乘加、关闭的工作状态。除此之外mode信号还控制着电源控制模块的状态,完成多电压控制。乘加器设计在200M频率下工作,在SMIC55nm工艺下,不同设计方案的模块综合面积见表1。其中分散模块指3种运算模块分开设计,并同时存在于设计中。

图1 多状态乘加器结构图

表1 不同设计方案的综合面积比较

本次设计的32位乘加器共分为4个步骤:

1)编写Verilog语言及Testbech完成电路逻辑设计实现仿真。

2)利用Synopsys的逻辑综合(design compiler, DC)的拓补模式将寄存器传输级(register transfer level, RTL)verilog代码转换为门级电路,同时插入UPF和scan chain分别对乘加器的电压供电情况和扫描链进行描述,并利用TetraMAX生成测试向量。

3)利用Synopsy的集成电路布局布线工具(integrated circuit compiler, ICC),最终生成GDS格式的版图。

4)利用Primerail对生成的版图进行功耗测试。

1.2 多电压综合

多电压设计,利用了UPF,其现在已经成为IEEE- 1801标准且为国际三大电子设计自动化(electro- nics design automation, EDA)厂商均支持的标准。在此使用UPF技术描述设计电路的电压工作状态,分别降低动态和静态功耗:

1)降低动态功耗

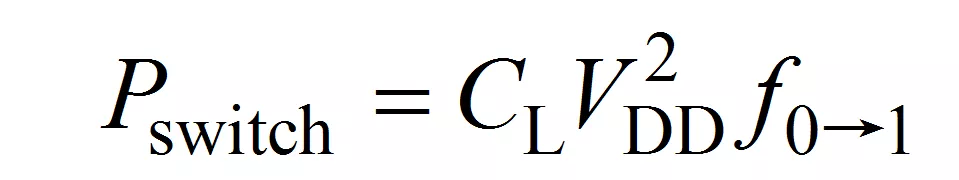

将需要资源需求较大的乘法划为高电压的电压域PDM,将在对于资源要求一般的加法器划为低电压的电压域PDA,其余模块会被EDA工具默认置入顶层模块所在低电压的PDT电压域,使不同性能需求的模块分别在高低电压下工作,从而降低动态功耗(dynamic power)。由于PDT和PDM的电压不同,因此还需对它们之间的输入输出信号插入电平转换单元(level-shifter),如图2所示。动态功耗的主要消耗为开关功耗。

公式1

图2 乘加器模块电压域图

2)降低静态功耗

要降低静态功耗可以在模块处于非工作状态时对其进行关断。这里需要插入和替换各种多电压器件:①电源开关将电压域的主电源关闭或打开;②保留寄存器可以在主电源关闭时以备用电源供电,以保留断电之前的数据;③隔离单元用于将关闭的电压域的数据进行稳定输出,防止不定态输出。

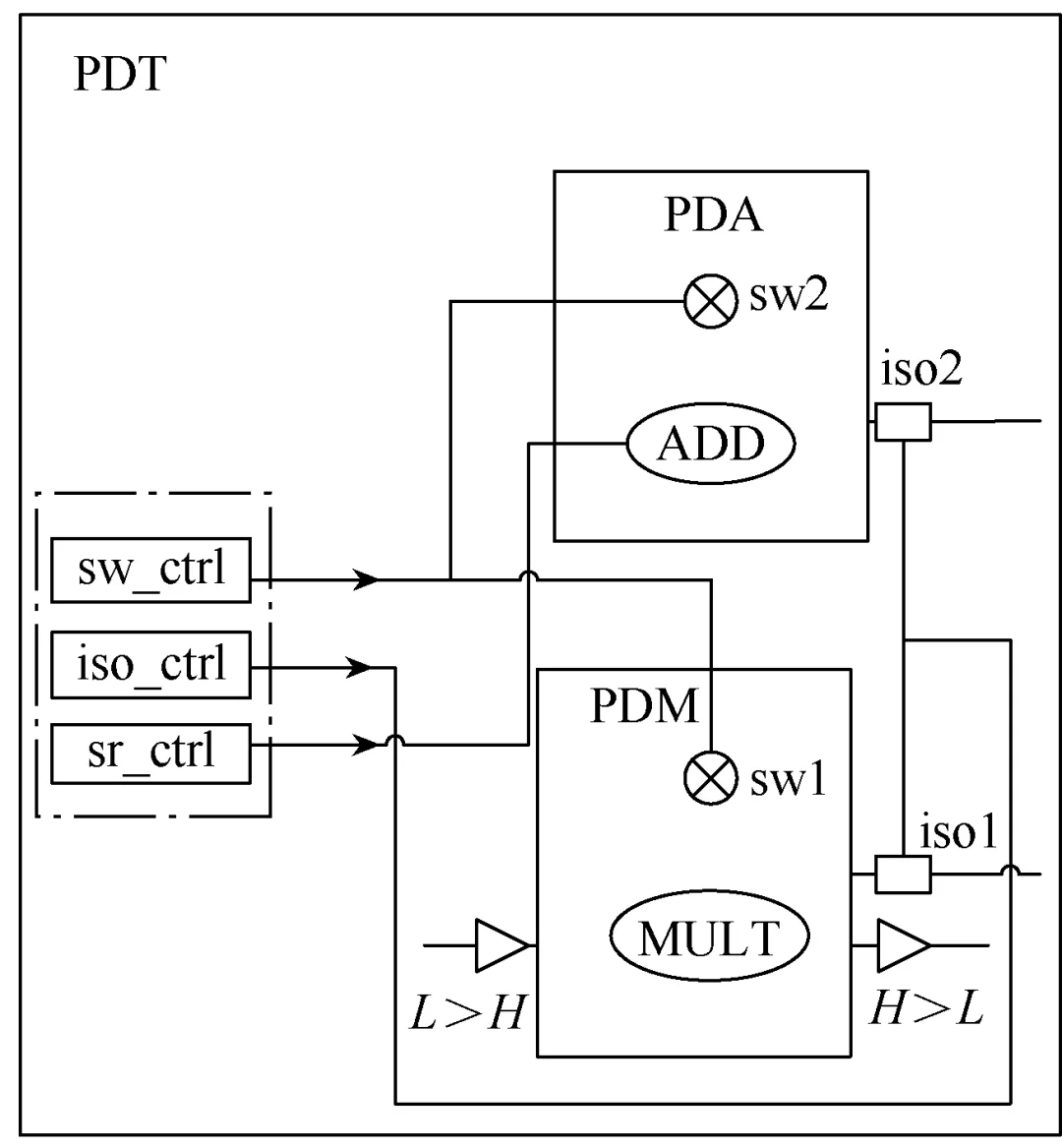

在RTL设计中电源控制模块控制着他们的工作状态,如图2所示,虚框内为电源控制模块。当一个模块要关断时,sr_crtl信号会先将保留寄存器切换至save状态以保存住这些寄存器的现时数据,并随后sw_crtl信号关闭电源开关,iso_crtl信号打开隔离单元承担数据的输出。

若要重新打开一个电压域,其保留寄存器要在电源开关开启后换至restore状态,读取断电前被保存的数据。最终,乘加器模块通过合理地开关各电压阈最终达到降低静态功耗(leakage power)的目的。

公式 2

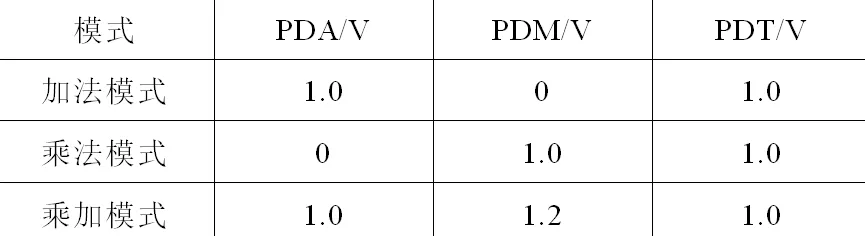

设计好各电压域工作状态后,还需建立电源状态表定义不同状态的各电压域工作电压,见表2,本次设计采用了多角多模(multi corner multi mode, MCMM)模型,为了验证不同电压下的工作情况,除了表中标出的电压外,还添加了上下两个相差10%的电压,以确保芯片在这些不同电压下均可以正常工作。

表2 乘加器电源状态表

1.3 电源控制模块封装扫描

扫描链测试的扫描方法实际上就是将各触发器加上一个数据选择器,使其拥有两个模式。第一个为正常模式,在正常模式下,所有的寄存器如同往常一样工作。另一种为扫描测试模式,实质上就是将触发器连接成多个移位寄存器,称为扫描寄存器。

在测试模式下,扫描时钟控制扫描寄存器,捕获输出信号后比对数据以检测寄存器是否正常工作,这样较大节省了测试时间和成本。

但与普通的可测试性设计不同,因为多电压设计中含有普通设计中没有的隔离单元,保留寄存器,电源开关,它们的工作状态均受信号的控制。但在扫描模式下,所有的寄存器的输出值均是由扫描信号扫描输入的,而与其在功能模式下正常工作不同,受控的保留寄存器和隔离单元会产生信号错乱,这些错误的信号控制着这些多电压器件工作状态,最终导致整个芯片在扫描模式下全部混乱。

因此在扫描链设计时,电源控制模块的扫描链需要单独设计。在此对两种不同的信号控制方法,一种外部输入并直接控制,另一种为信号控制模块在芯片内部,对二者扫描链设计有两种不同的设计方案。

1)信号由外部输入时

可以将外部输入的多电压控制信号设置为Constant模式,将信号固定在0或1值,这样就使各种多电压等在DFT测试阶段均不做信号改变的动作,再按常规步骤对剩余电路进行扫描链设计。

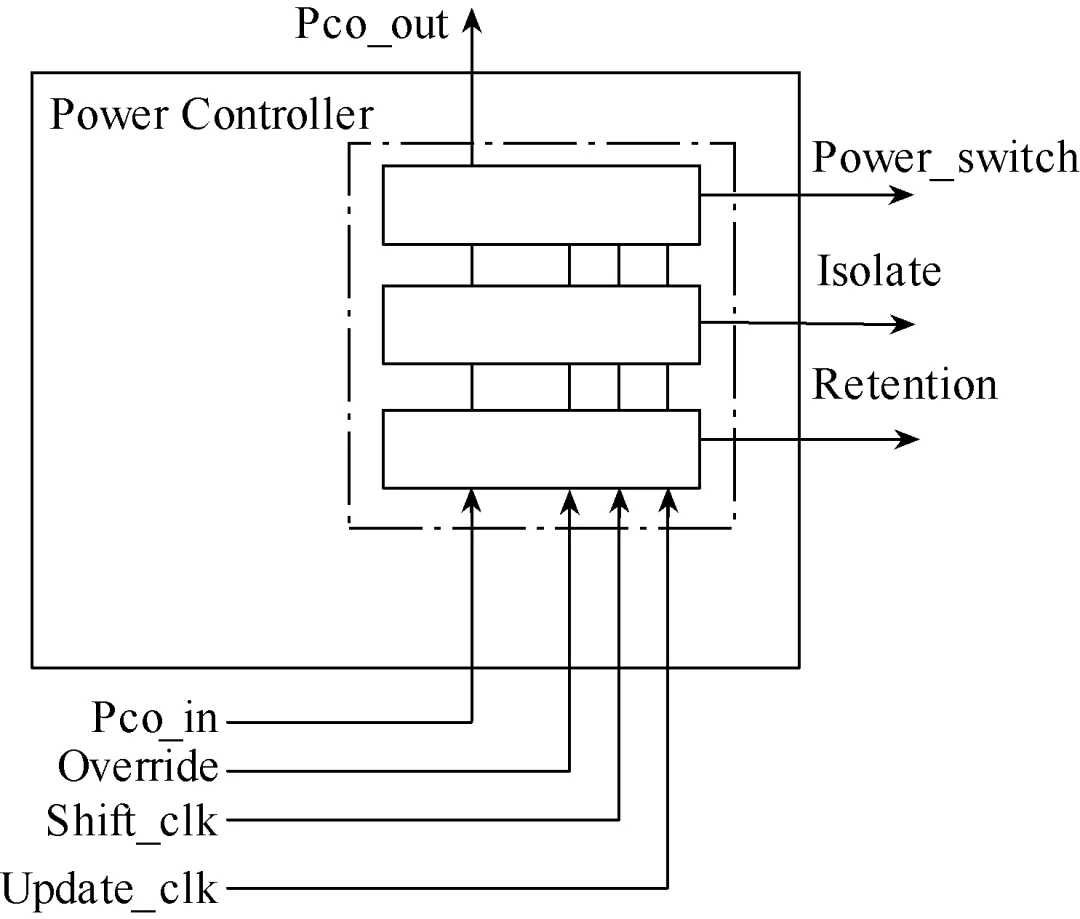

2)电源控制模组在芯片内部

如本设计,若电源控制模组在芯片内部时,如果将其模块的控制信号输出值固定,这样虽然不会打乱受控多电压器件的工作状态,但是也无法对电源控制模组进行扫描测试。因此需要将内部的电源控制模块单独封装为一个封装扫描链,进行测试,如图3所示。

图3 电源控制模块封装扫描链设计图

其原理其实就是将电源控制模块的输出部分封装,并与芯片内其余的扫描链分开,形成一条单独的扫描链,并且此扫描链的时钟也不是其余扫描链模块共用的扫描时钟,而是一个单独时钟shift_clk,并由update_clk和override信号的组合控制使其控制的多电压器件可以正常工作。最终实现对整个芯片各个模块的测试覆盖,并且不会产生信号混乱的问题。

但这条特殊的扫描链不能与其余扫描链压缩在一起,所以需要单独的扫描IO端口。但对于乘加器模块来说,其IO端口多达几十个,在扫描模式中,不用从功能模块的IO端口中输入输出。因此在扫描链设计时,各种额外的端口可以借用功能模式下的IO端口,利用一个数据选择器进行复用,这样可以节省IO端口的使用,从而也可以节省芯片的面积。

使用TetraMAX软件,对插入扫描链后的电路进行自动测试向量生成。运行结果表明,扫描测试的测试覆盖率为96.8%,满足设计要求。生成的测试向量将在芯片生产后供测试使用。

1.4 物理设计

将插入综合好的verilog、UPF、scan_def和sdc格式的文件分别读入ICC后,对其进行数字版图设计。在整体布局上,由左输入,由右输出,输出数据先经顶层模块到乘法器模块,再连接加法器模块,最后由输出端口输出。

除了常规的数字版图流程外,还要创建voltage area与在UPF定义的power domain的对应。前者是在物理设计中真实存在的电压区域,需要定义大小、高度、位置,而后者则仅仅是对其电压模块的逻辑电压定义。

在此voltage的区域与乘法器模块区域完全重叠。多电压器件的电源开关也要在物理设计确定具体的位置,而不是由工具自动摆放,因此要确保需要关断的电压域PDA和PDM内每个标准单元的主供电电源都连接到电源开关。

乘加器模块的供电方式采用了电源环外围供电与电源网格供电,供电电压分别为高(1.1~1.32V)、低(0.9~1.08V)、地(0V)3个电压,其中乘法器模块工作在高电压的工作模式下,整体布局图如图4所示。再经自动布局布线(place and route, P&R)过程后最终生成GDS版图。

图4 多状态乘加器物理设计布局图

2 功耗分析

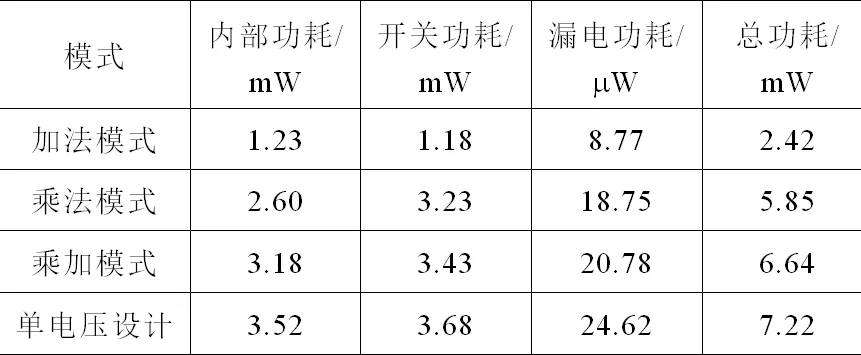

乘加器设计在200M频率下工作,乘法器工作在1.08V,加法器工作在0.9V时,利用Primerail工具进行评估,并调用SMIC55nm工艺库标准单元,其布局后功耗见表3。

表3 不同模式功耗消耗

由表3可见,在多电压设计下,芯片运行在全负荷的乘加模式仍比单电压设计节省功耗8.0%,除此外,多电压设计还可以根据需要对不同模块按需进行开启和关断,更彻底地降低功耗。

3 结论

本文简述了多电压设计与扫描链设计在一个可以切换工作状态的32×32乘加器设计同时应用的方案。该方案结合了UPF和scan chain技术的概念及使用。

前者可以对不需要工作的模块进行电源关断降低静态功耗,及将不同性能的模块分高低电压处理降低动态功耗;后者可以实现在裸片时对芯片进行测试验证其好坏。两种技术可以在牺牲较小的面积的前提下同时实现。

电厂关键技术研究及其应用”专题征稿通知.jpg)